DFT Interview Series : Article #1

What does the Tessent Scan tool do during scan insertion if the design contains shift registers?

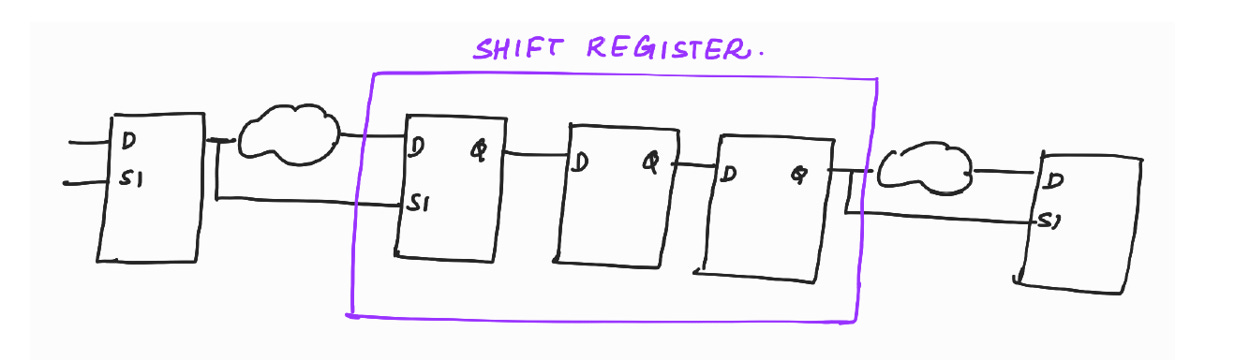

When the design contains shift registers, the tool replaces only the first flip-flop in the shift register with a scan flip-flop (since it must select between the D and SI inputs).

The remaining flip-flops in the shift register remain as normal flip-flops because, even if converted to scan flip-flops, their D and SI inputs would be same. Converting them would require additional multiplexers, leading to unnecessary area overhead. To avoid this, the tool retains the other flip-flops as normal flops.

Shift register flops will also be a part of scan chain.

Why do we have non-scan flops in the design?

Reason 1 :

If a flop has clock controllability (or) set/reset controllability DRC, and if it is not fixed, it will not be converted to scan flops.

Reason 2 :

In certain situations, the designer would have specified that these flops should not be scanned :

The flops which hold some encryption data. The designer will ask us not to scan those flops because, if it is scanned, the encryption value will be shifted out. But it is a protected data. So those flops will not be scanned.

The flops that are used for security reasons.

For example, some flops will be used to lock JTAG.

Suppose Company A is selling their chip to Company B, Company A will lock their JTAG.

Suppose those security flops were scanned, then there is a possibility that Company B can shift some values into those flops and remove the JTAG lock and Company B will take the proprietary information of Company A’s chip.So, the security flops will not be scanned and it will be designed in such a way that their clocks are also gated during scan operation so that their values can’t be disturbed by anyone.

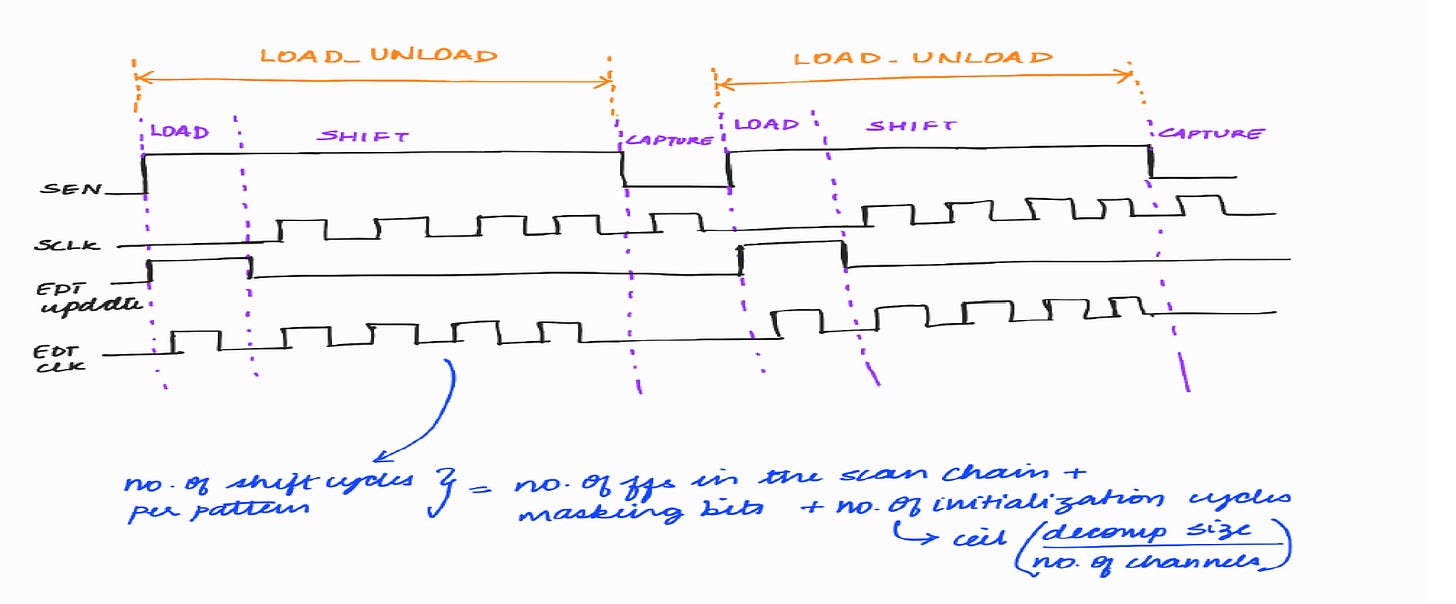

In the below waveform,

Why EDT_clk is not pulsed during capture?

Capture phase is to capture the response of the combo logic.

In EDT, there is no significance of this phase because EDT is used to decompress and shift appropriate pattern into the scan chain, and to compress the values shifted out by the scan chains.

So EDT_clk (the clock to the EDT logic flops) is not pulsed during capture.Why SCLK (Scan Clock) is not pulsed during load phase?

Consider the second shift phase. During the second shift phase, the captured value of Pattern 1 will be shifted out and simultaneously Pattern 2 will be shifted in.

Suppose SCLK (slow frequency clock that goes to SFFs) is pulsed during load phase, then the captured value of the SFFs will get shifted out in the load phase itself.

But captured value of SFFs should get shifted out in the shift phase. So SCLK is not pulsed during load phase.In this blog, we have explored some application oriented interview questions from scan insertion and scan compression topics.

In the upcoming blogs of the DFT Interview series, we will explore many more application oriented interview question from the topics which is discussed in the DFT Basics series.

Stay Tuned !