Answering Curious Minds

Breaking Down Reader Queries

In DFT Basics: Article #4, we explored Clocks and Clock Gating.

In DFT Basics: Article#18, we discussed Fault Simulation and ATPG Pattern Generation.

In this post, we will take up an interesting reader’s question:

“How do we cover the faults on the Functional Enable (FE) pin of a Clock Gater, given that the output of the Clock Gater is a clock signal and not a logic value that can be directly observed on a Scan Flop?”

To get the full context, I recommend reading the two posts linked above before continuing with this one.

NOTE :

Keep going till the end, where a waveform will help us visualize and consolidate the discussion.

We will also uncover an important aspect:

the advantage of connecting the Test Enable (TE) of an Integrated Clock Gater (ICG) to the Scan Enable (SE).

This will not only help us understand how to handle fault coverage on the FE pin but also highlight a best practice widely used in DFT.

Let’s get started !

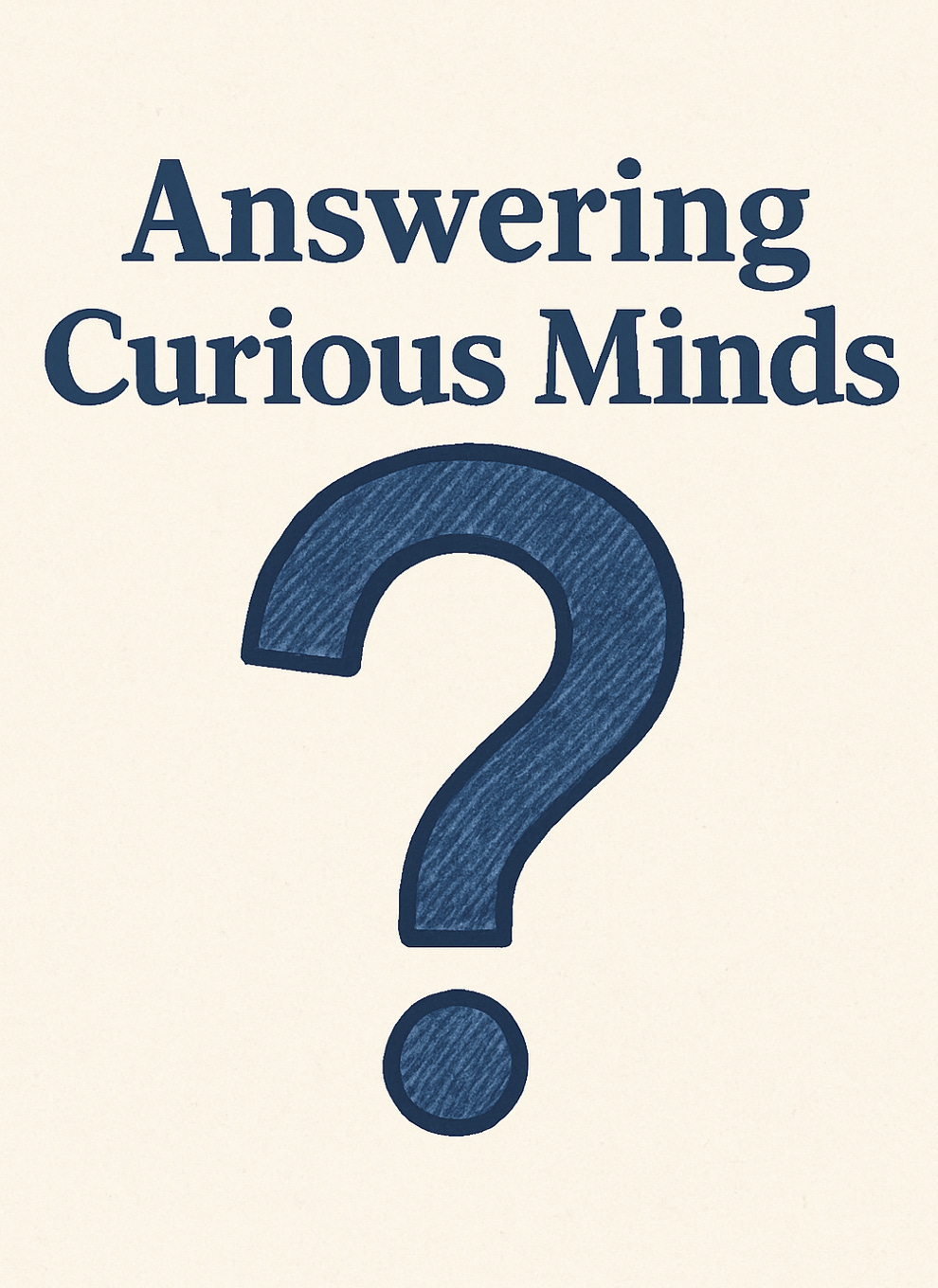

Connecting Test Enable (TE) of ICG to Test Mode (TM) signal

Throughout DFT, Test Mode (TM) = 1

Therefore tool will be able to detect only SA0 on Test Enable (TE) net.

And the faults on the Functional Enable (FE) net will be blocked.

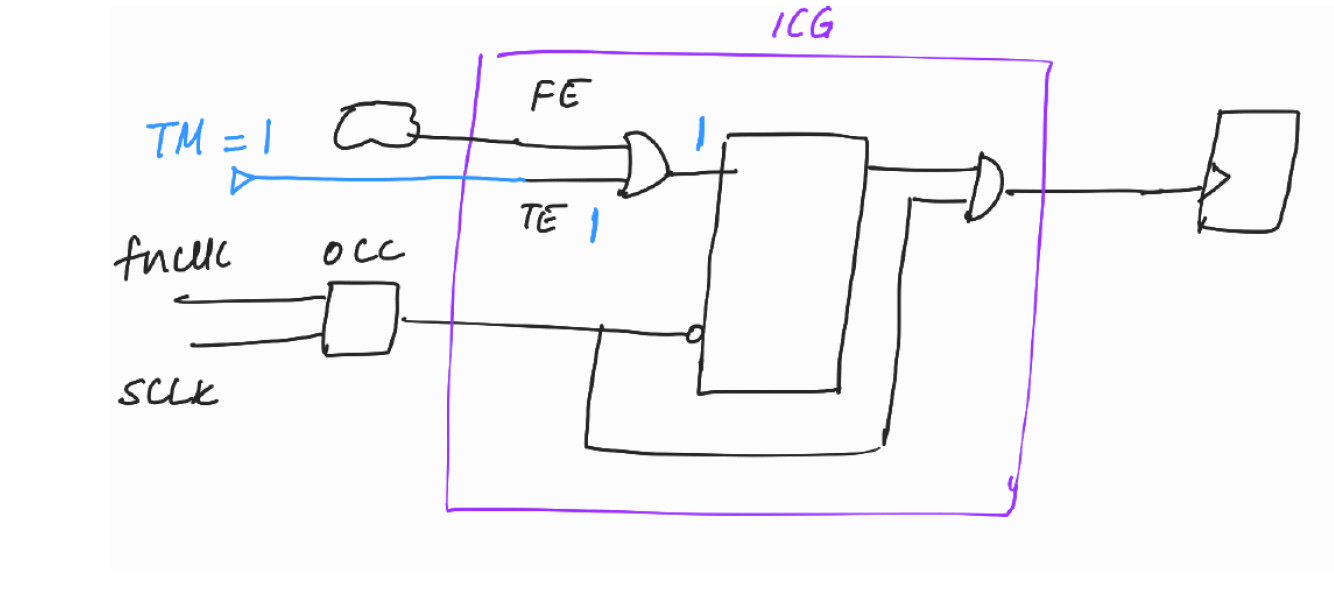

Connecting Test Enable (TE) of ICG to Scan Enable (SE) signal

During Shift Phase,

Scan Enable (SE) = 1

As seen from the above waveform, clock will be propagated to the flops during shift phase.

And SA0 on Test Enable (TE) of Integrated Clock Gating Cell (ICG) can be detected.

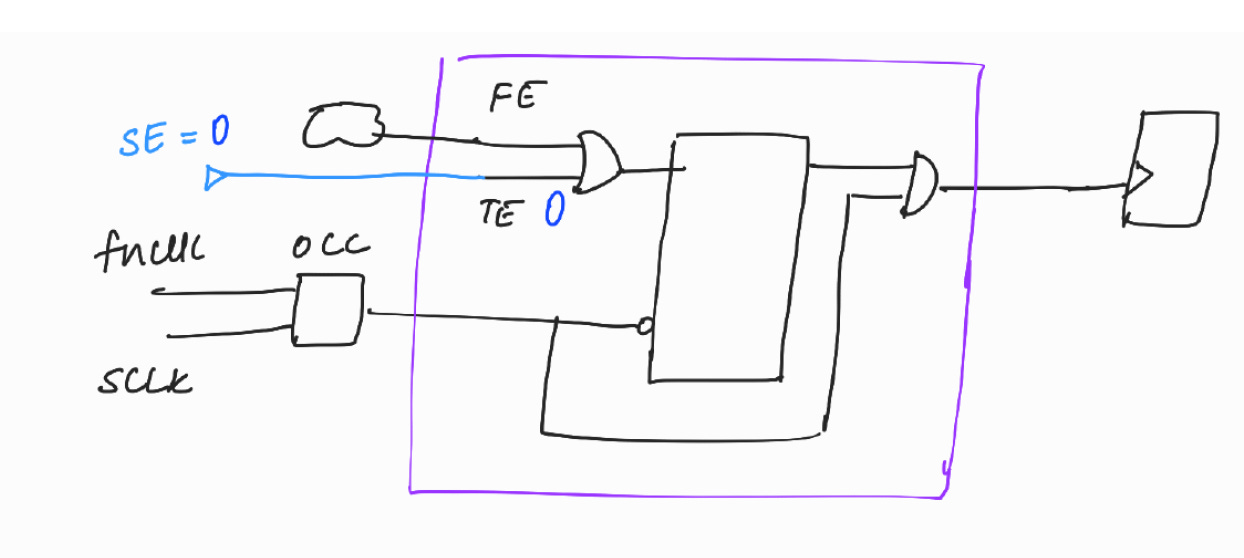

During Capture Phase,

Scan Enable (SE) = 0

SA1 on TE of ICG can be detected

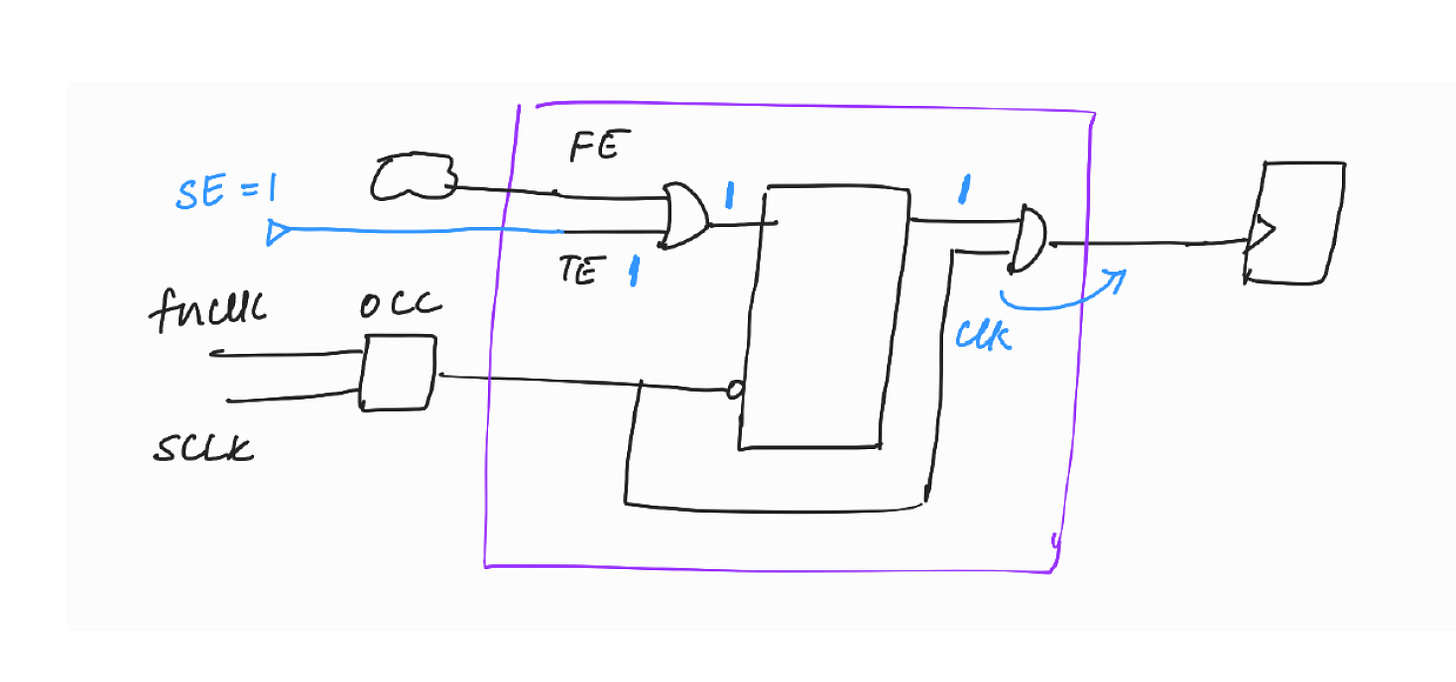

Covering Faults on Functional Enable (FE) :

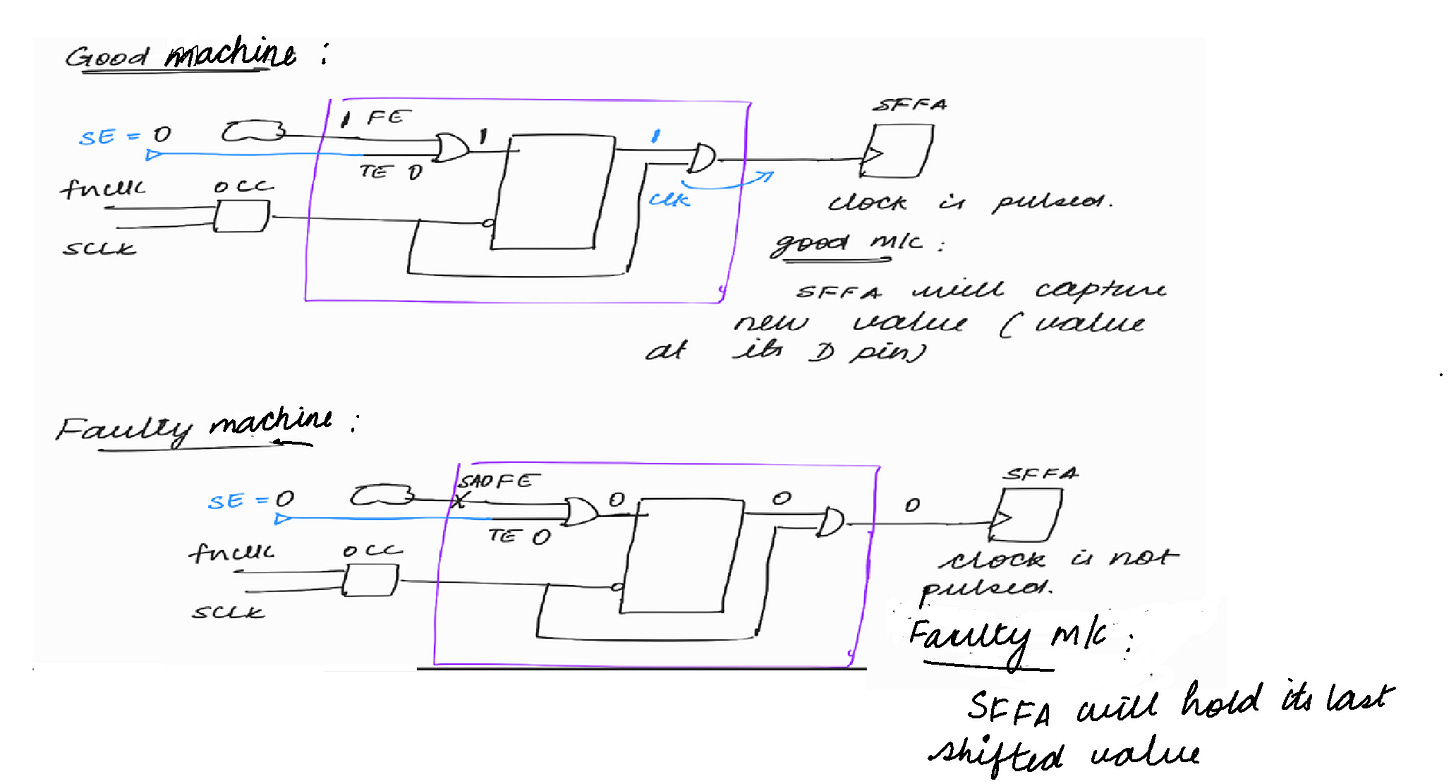

To detect SA0 on Functional Enable (FE)

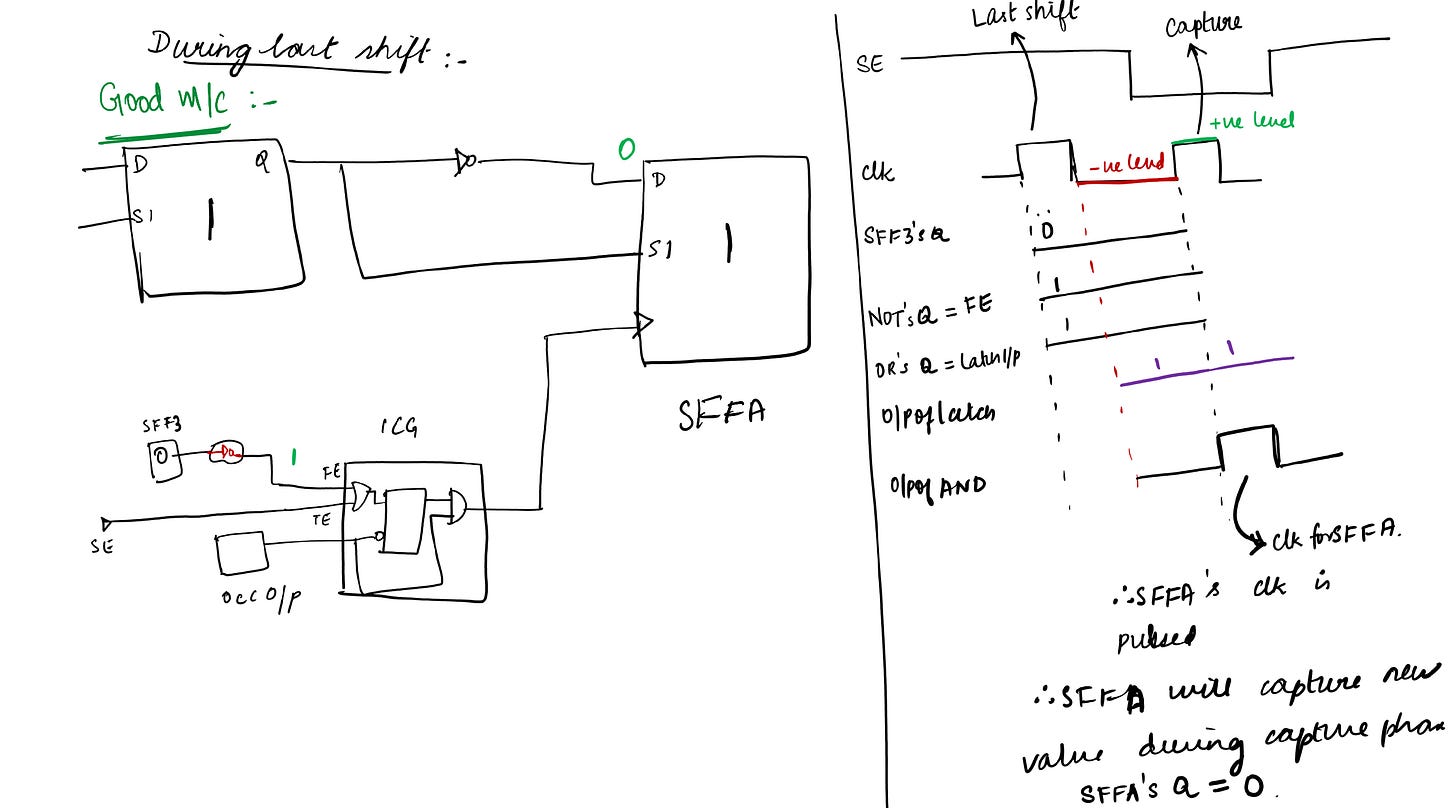

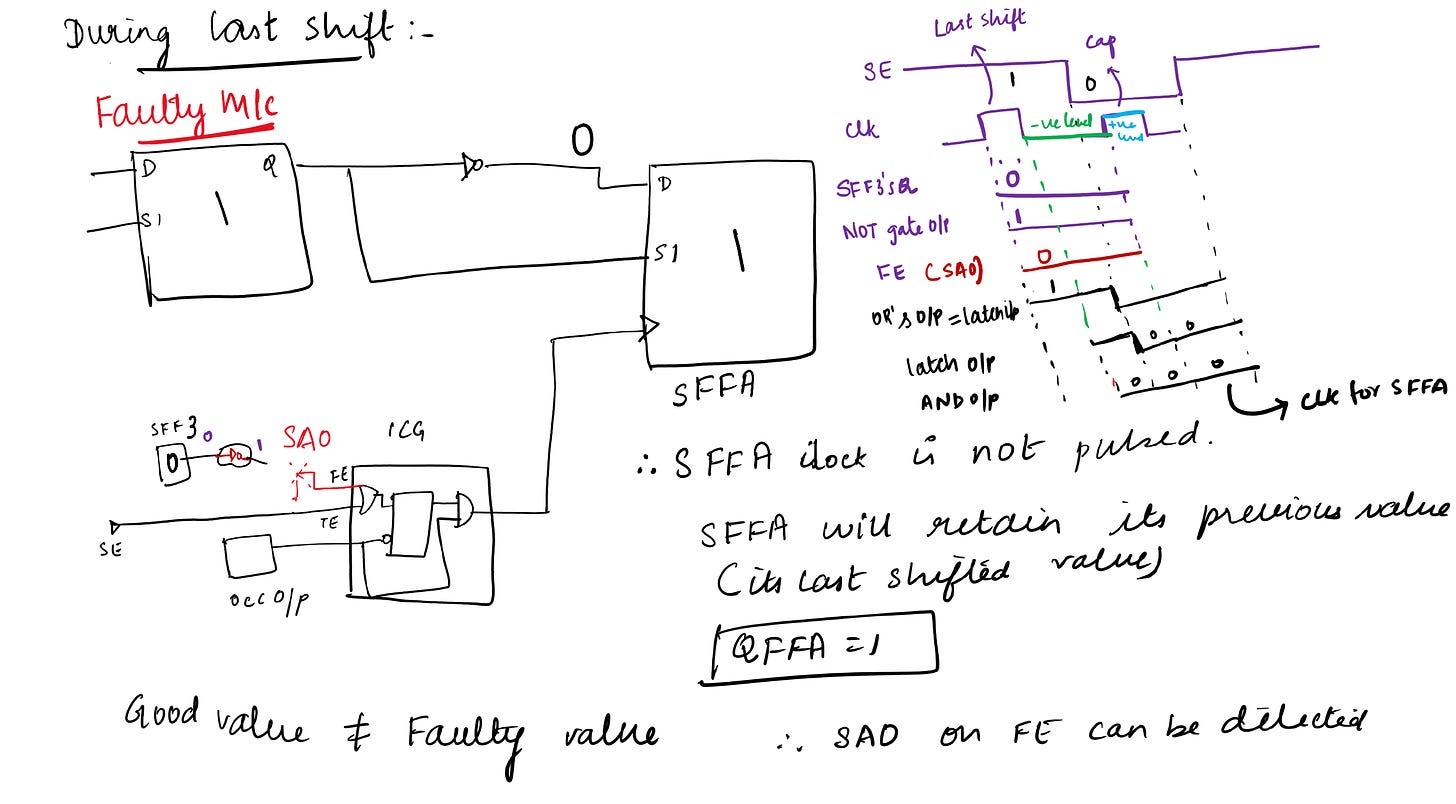

For a clearer picture, let’s examine the above illustration step by step using a waveform.

Good machine Simulation :

Faulty machine Simulation :

The same process can be extended to SA1 on Functional Enable (FE) of ICG.

In this blog, we have explored how the faults on Functional Enable (FE) of ICG is covered.

We have also explored the advantage of connecting Test Enable (TE) of ICG to Scan Enable (SE) signal.