Hierarchical Scan Part 2

DFT Basics : Article #20

In my previous blog DFT Basics : Article #19, we had explored Shared and Dedicated Input and Output Wrappers.

In this post, we will explore the various concepts of Hierarchical Scan like Intest, Extest and pattern re-targetting.

Let’s get started !

DESIGN :

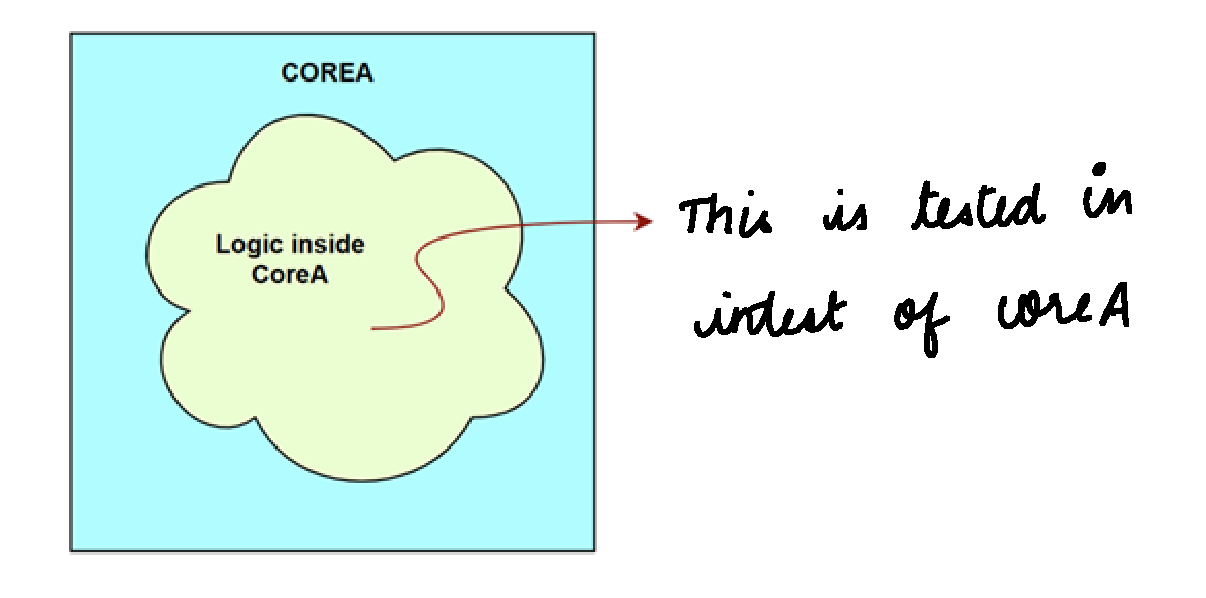

CoreA intest

• To test the internal logic of CoreA.

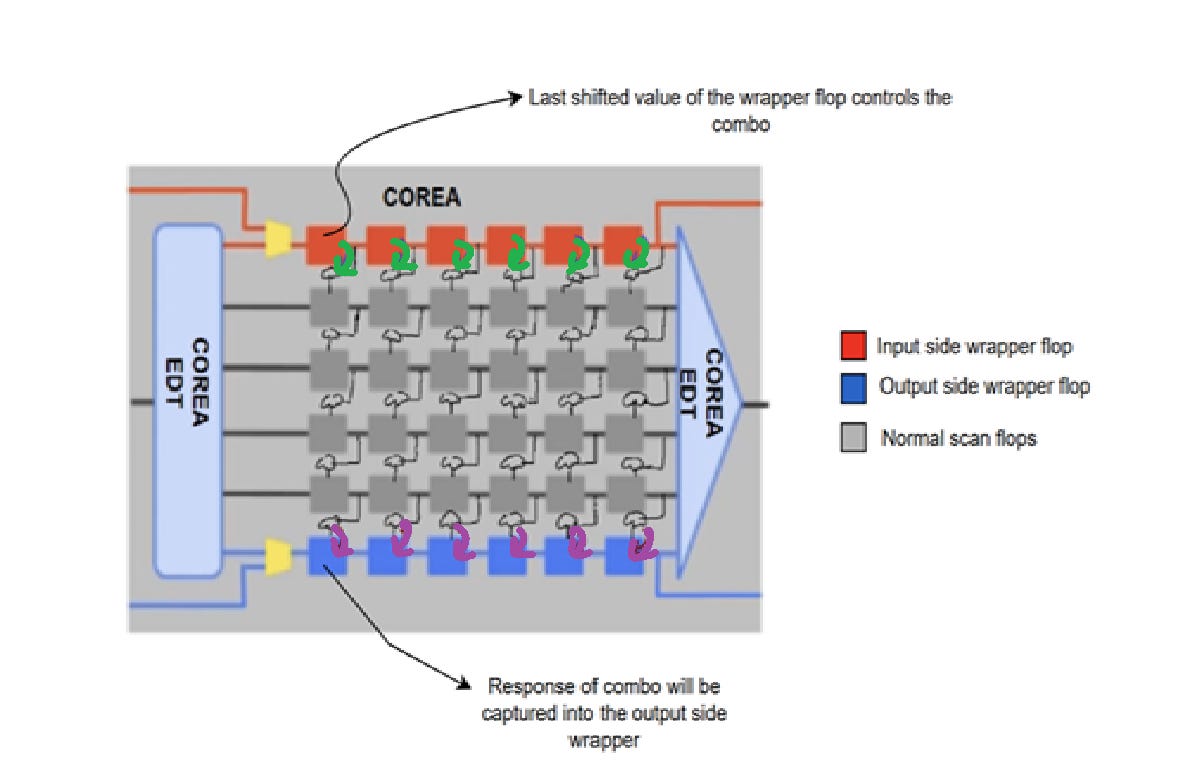

• CoreA’s EDT controls CoreA’s normal SFFs and CoreA’s wrapper flops.

<< For a detailed explanation of EDT logic, please see DFT Basics, Articles 11 to 17 > >

Role of CoreA’s wrapper flops during intest of CoreA :

Input wrapper chains launch data into the inside logic and output wrapper chains capture data from inside logic (as depicted by arrows in the figure).

During this time, the input sequence will be shifted into the wrapper chains by CoreA EDT.

< < We have already explored this in detail in DFT Basics : Article #19 > >

Normal Scan Flops will be doing their usual operation (shift, capture, shift-out)

< < We have already explored this in DFT Basics : Article #2> >

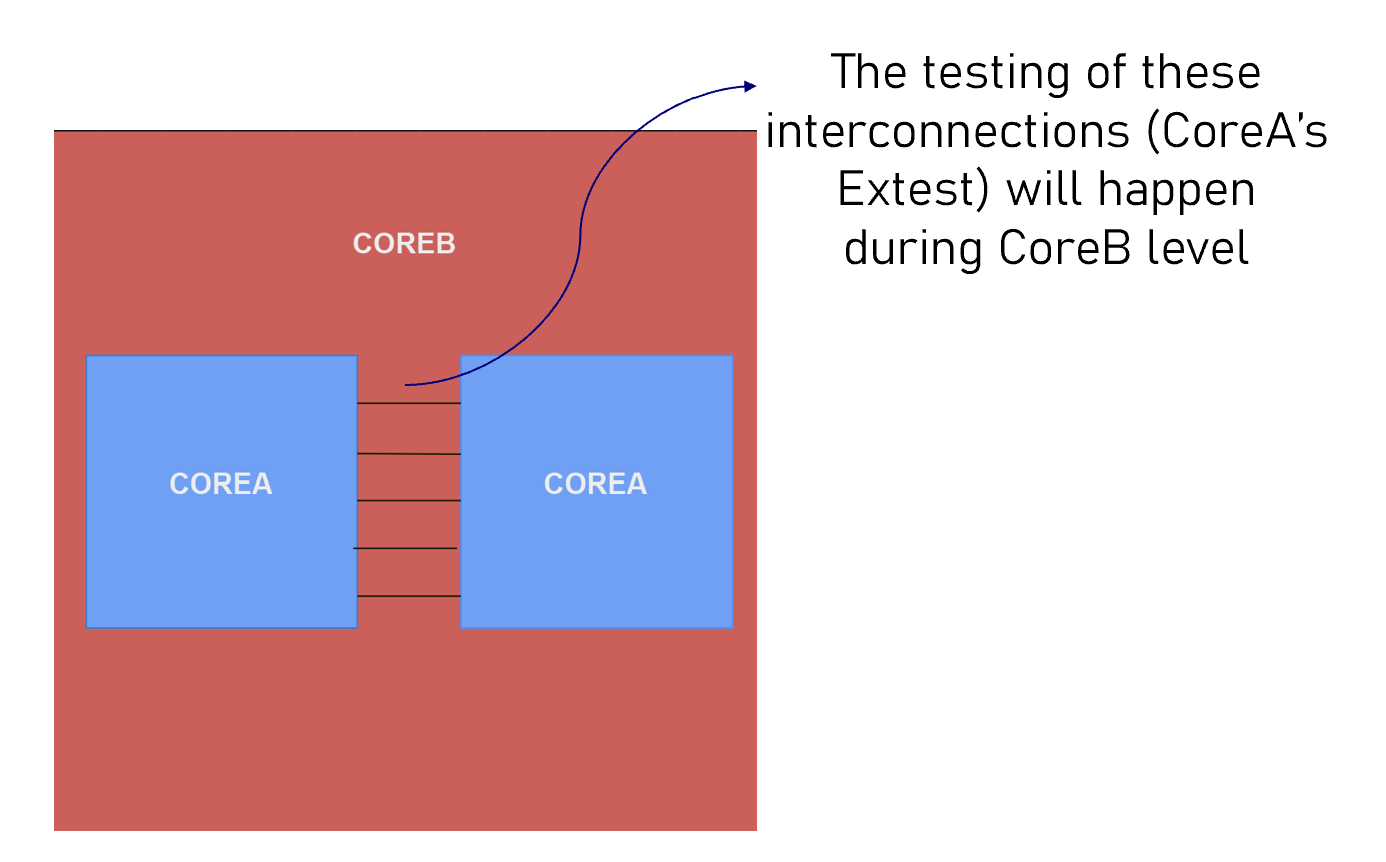

CoreA extest

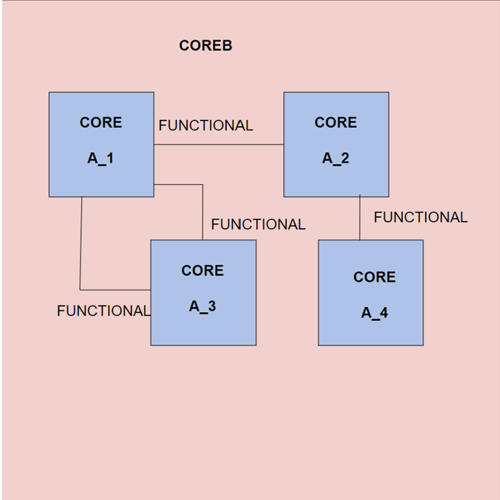

• The testing of interconnections between CoreAs (extest of CoreA) will happen in the CoreB level.

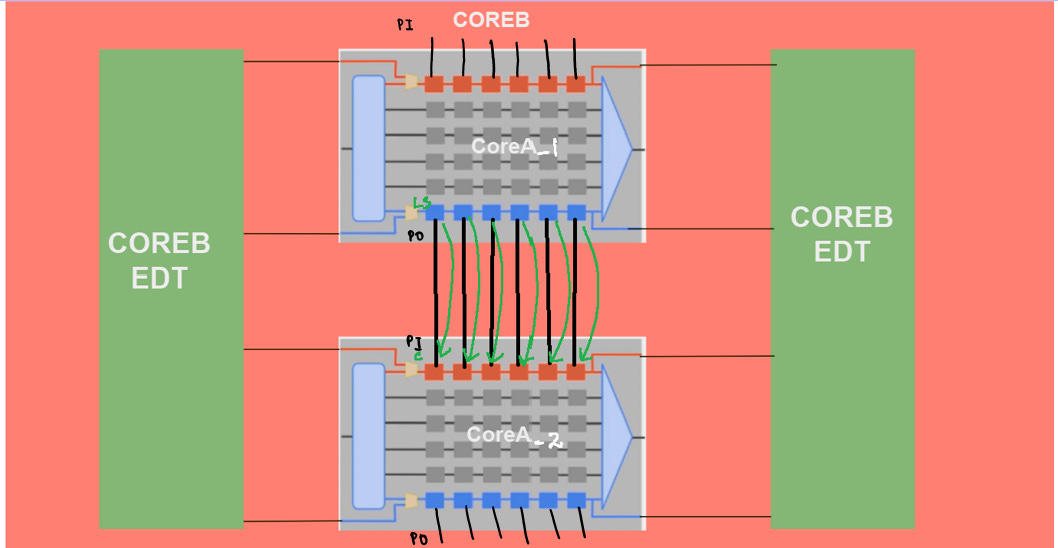

• Last shifted value of CoreA_1’s output side wrapper (blue colour) will be captured into CoreA_2’s input side wrapper (red colour) (As depicted with green lines in the below figure). If there was some defect in the interconnection, then wrong value will be captured.

• During this time (CoreB level), CoreAs will be in extest.

CoreB’s EDT will be shifting the values into CoreA’s wrapper flops.

< < We have already explored this in detail in DFT Basics : Article #19> >

<< For a detailed explanation of EDT logic, please see DFT Basics, Articles 11 to 17 > >

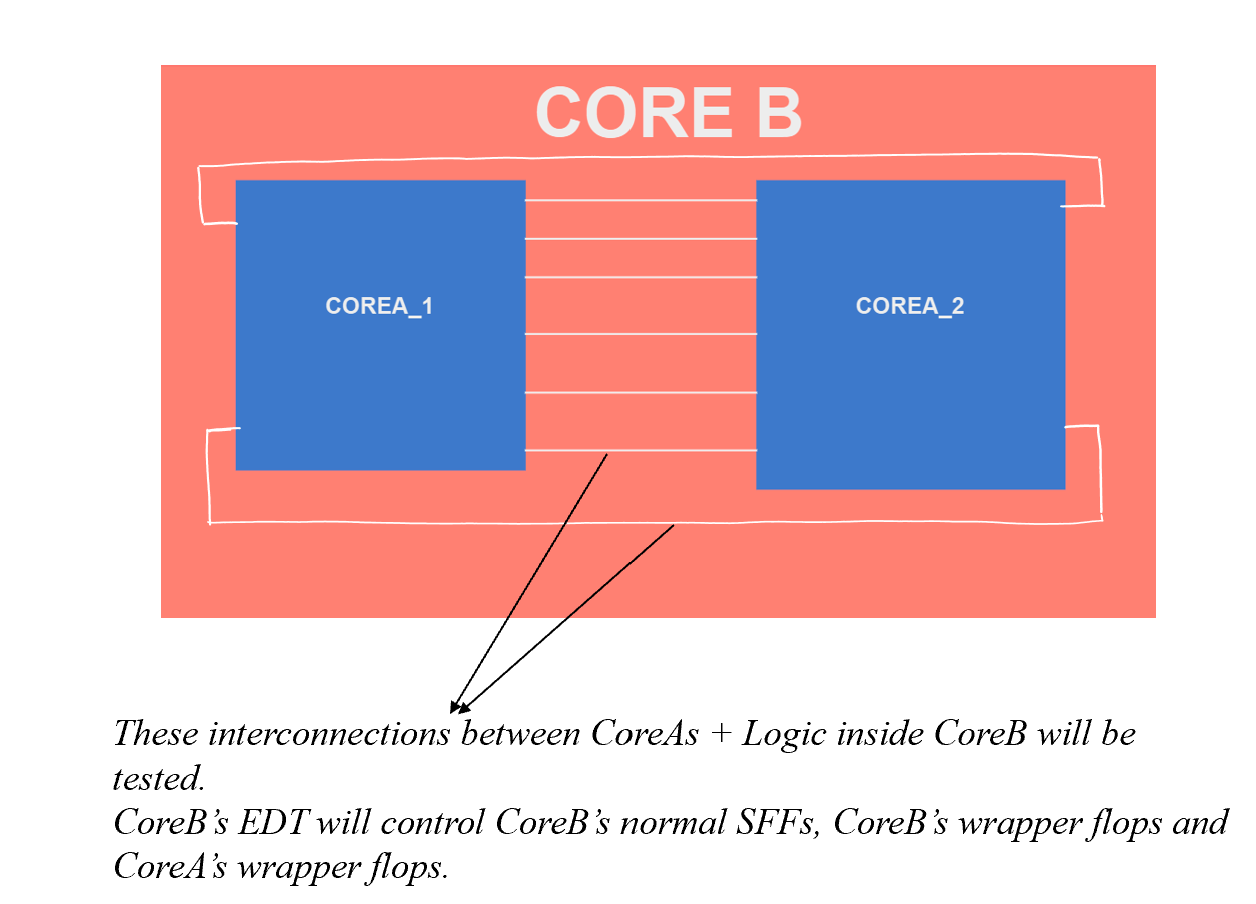

CoreB intest

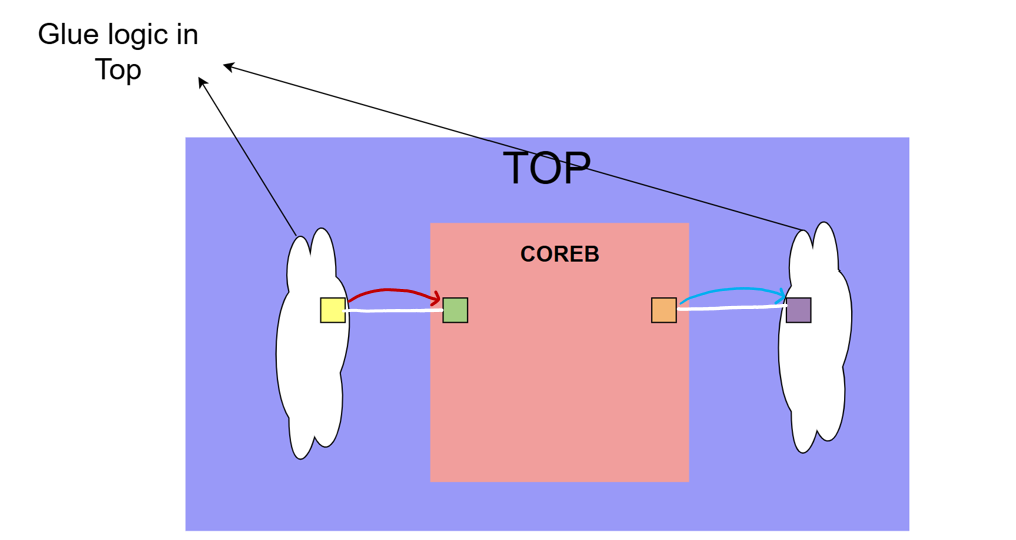

CoreB extest run

• CoreB extest happens at top level.

• Last shifted value of flop in glue-logic in top will be captured by input side wrapper flop of CoreB (depicted by red arrow in the figure). Similarly last shifted value of CoreB’s output side wrapper will be captured by the flop in glue-logic in Top (depicted by blue arrow in the figure). If there is any defect in the interconnection, then wrong value will be captured.

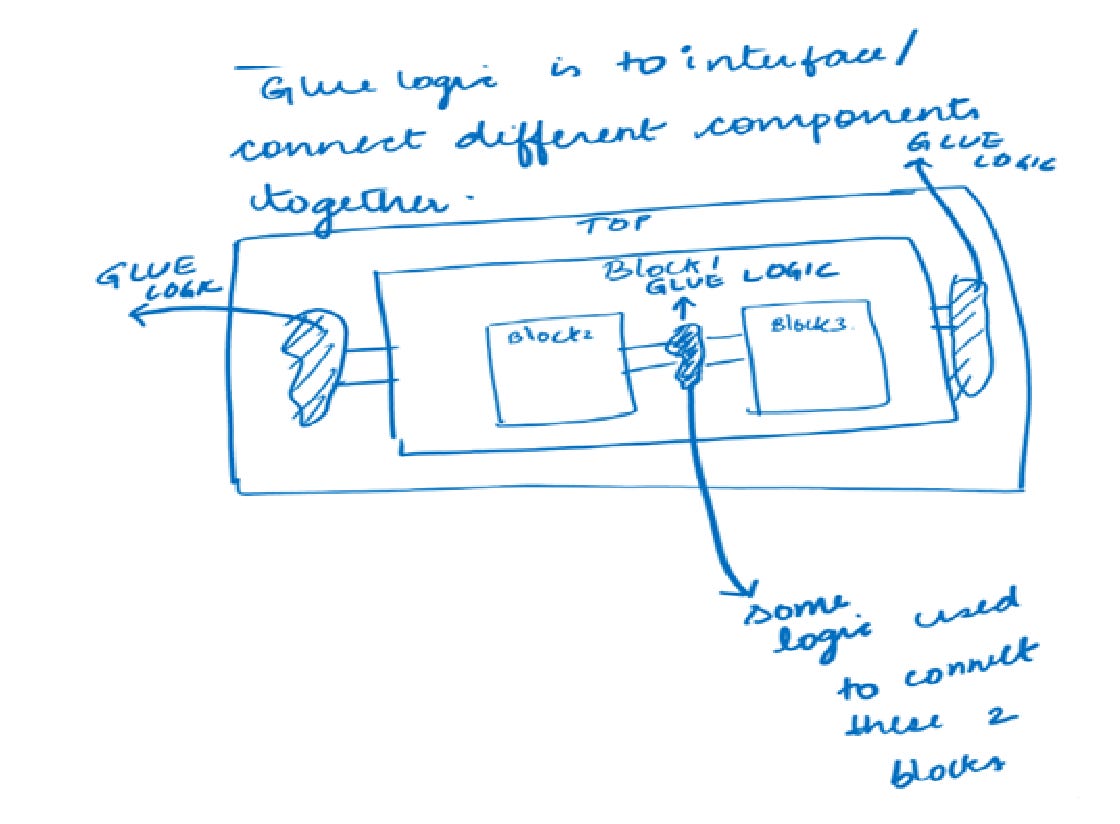

What is a glue logic?

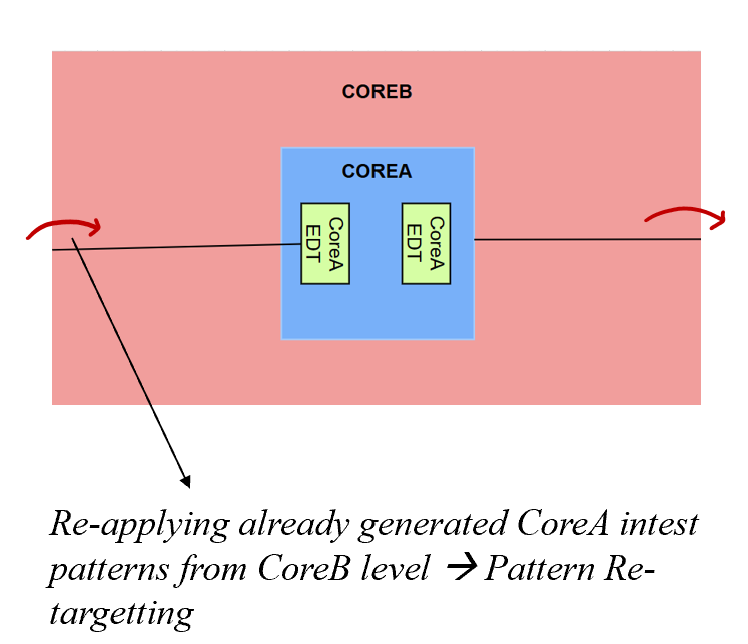

Pattern re-targetting

Re-applying already generated CoreA intest patterns from CoreB level instead of generating it again.

Note :

After top insertion, CoreA intest patterns will be again re-applied from top level also.

Why pattern re-targetting ?

Finally at the tester level, everything has to be applied from top level.

Why only CoreA intest ?

CoreA extest (interconnections) are already tested at the CoreB level and patterns are generated from CoreB level.

Thanks for post , i just want to know can we share input and output wrapper chains ?