DFT Interview : Article #3

Welcome to the third post in DFT interview series!

You can also explore DFT Interview : Article #2

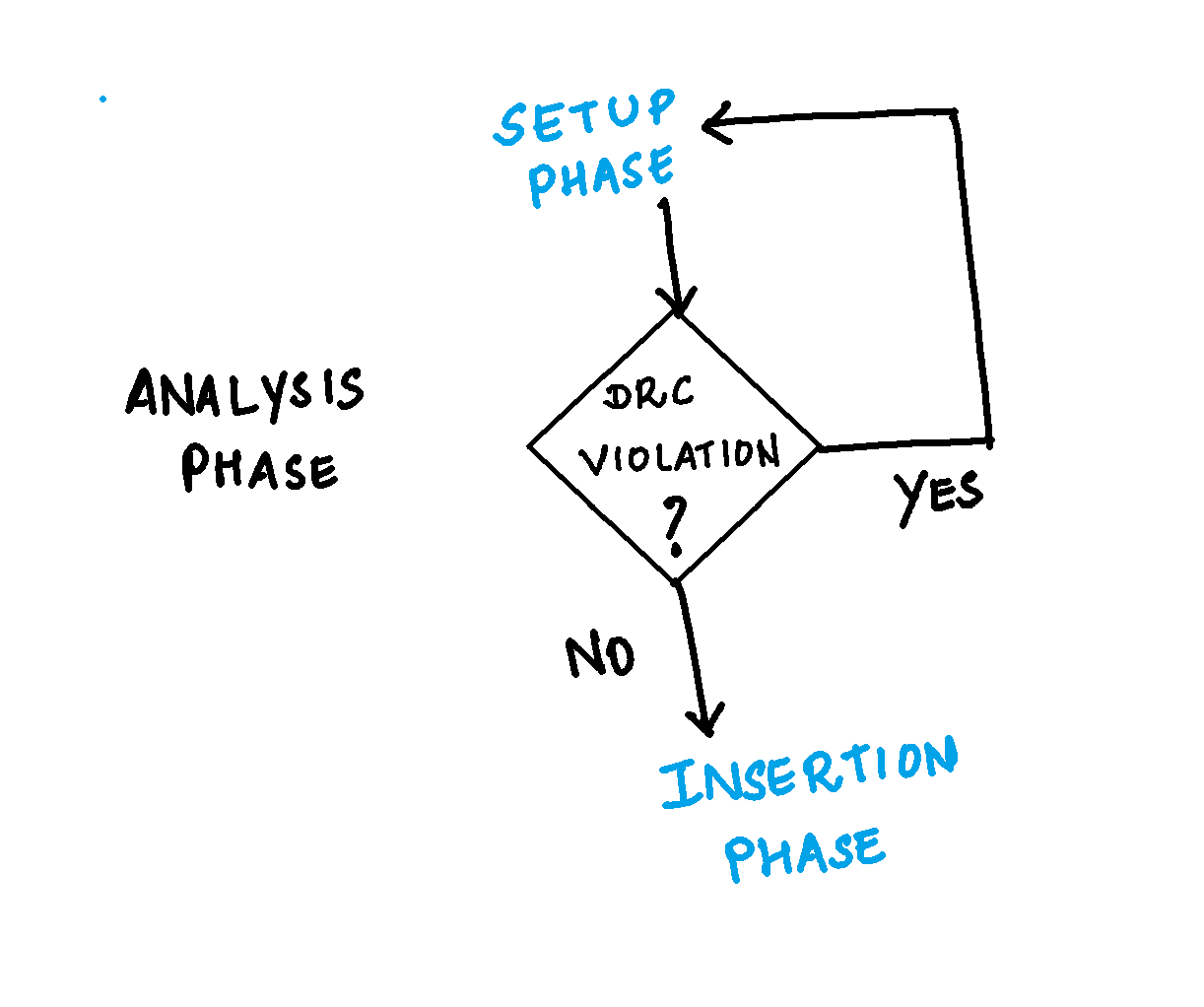

Q1 : What is the flow of Scan Insertion in Tessent tools?

Ans :

Setup Phase -

Reading the input files and library files.

Elaboration

- - tool checks if the module definition of all modules is available.

- - tool checks if all the module instantiations are correct.

Provide the declarations and constraints.

Analysis Phase -

DRCs are checked.

< < Design Rule Checks, DRCs, are the set of rules which each flop in the design has to pass in order to be scannable > >

If there are any DRC violations, go to the setup phase and fix the DRC violations.

If there are no DRC violations, go to the insertion phase.

Insertion Phase -

Identify the scan equivalent.

Replace all the normal flops with scan flops and stitch the scan chains.

Write out the reports and outputs of scan insertions.

Q2 : Why is scan insertion performed on gate level netlist?

Ans :

In RTL, we don’t have a physical impression of all flops. RTL can also be written with parameters stating multiple flops with single always command. It is difficult to modify such code lines and add mux to it to make it a scan flop.

Q3 : What are the DRC violations you have encountered while performing scan insertions using Tessent tools?

Ans :

S1 violation :

We get S1 violation when

clock and set/reset declaration is wrong or missing.

clock or set/reset of a flop is controlled by another flop or any combo logic’s output.

set/reset of a flop is tied to a fixed value.

S2 violation :

We get S2 violation when

clock of a flop is tied to a fixed value.

D5 violation : Gives a list of non-scan memory elements

We get D5 violation when

a flop has S1 or S2 violation.

a flop’s scan equivalent is not available in the library file.

if it is a latch.

C6 violation : Clock Data race DRC violation

We get C6 violation when the clock signal goes to the clock pin and D pin of a flop.

E10 violation : Bus contention violation

We have explored all the above DRC violations and their fixes theoretically in Scan DRC (part 1) and in Scan DRC (part 2).

Q4 : What is the auto-fix command in Tessent tool to fix the above DRC violations?

Ans :

set_test_logic command

-clock on : fixes the clock controllability DRC violation

-set on : fixes the set controllability DRC violation

-reset on : fixes the reset controllability DRC violation

-tristate on : fixes the bus contention violation

-C6 on : fixes the C6 violation

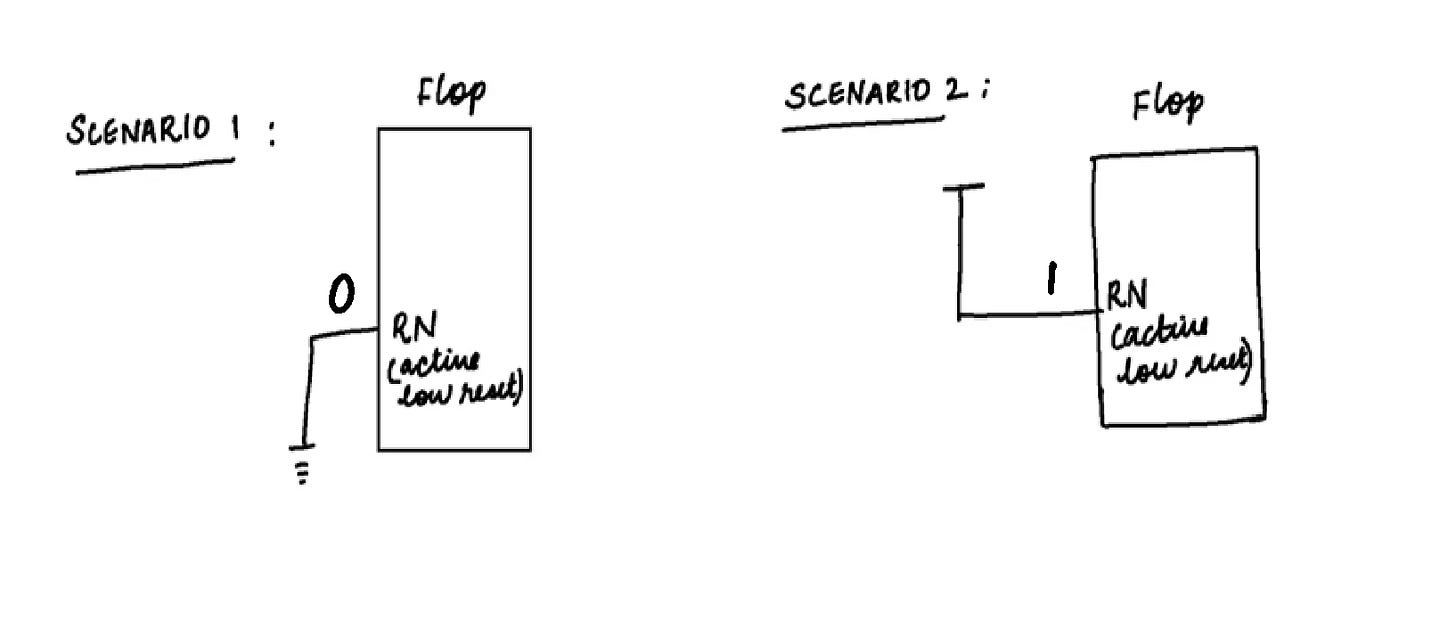

Q5 : Consider the below 2 scenarios :

In both the cases, Reset of the flop is tied to a fixed value.

Tessent tool points Scenario 1 as S1 violation. But it doesn’t point Scenario 2 as S1 violation.

Why?

Ans :

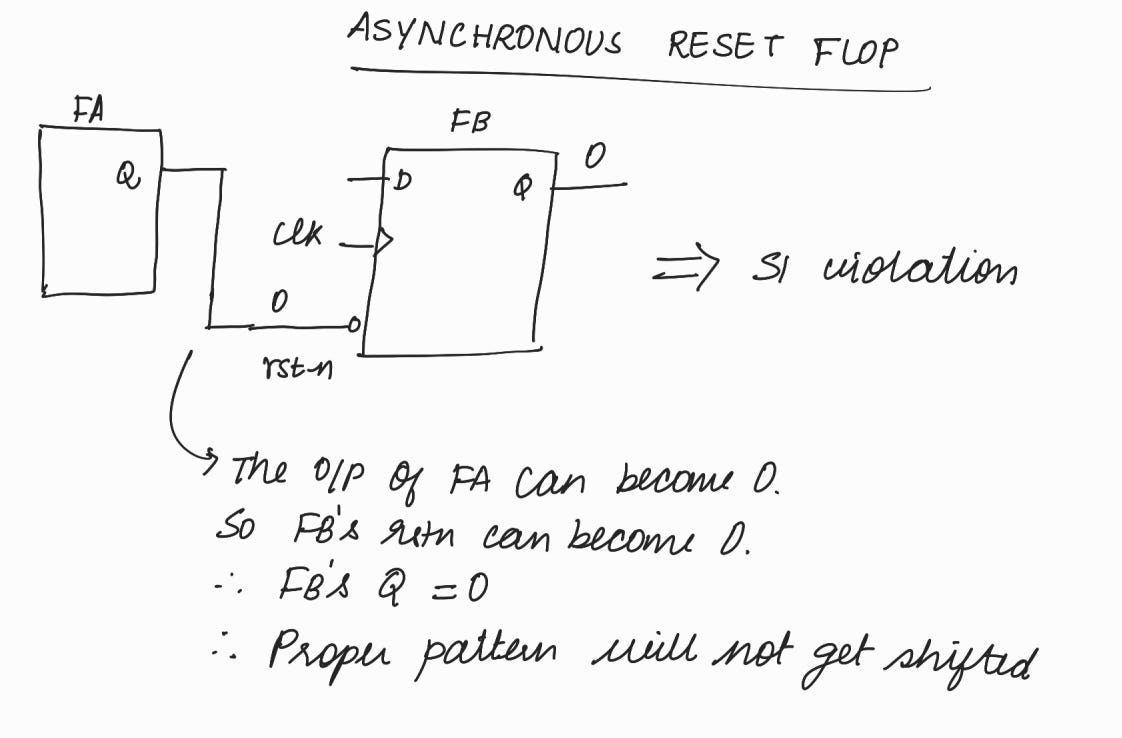

Scenario 1 :

It is an active low reset flop.

It’s reset pin is tied to Gnd. So the flop’s output goes into a reset state i.e., Q = 0 (since it is an active low reset flop)

It will affect the state of the flop during shifting (i.e., proper patterns will not get shifted into the scan chains).

So it is pointed as S1 violation.

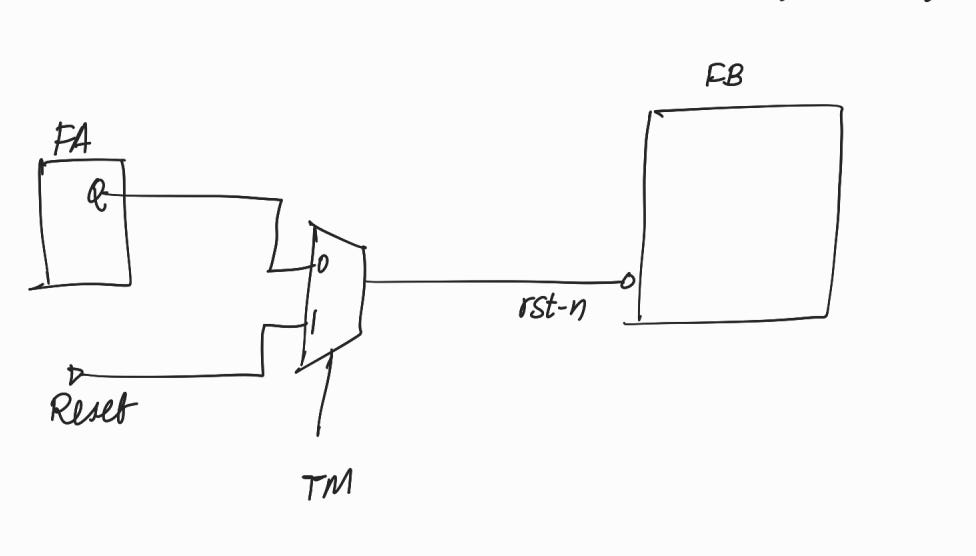

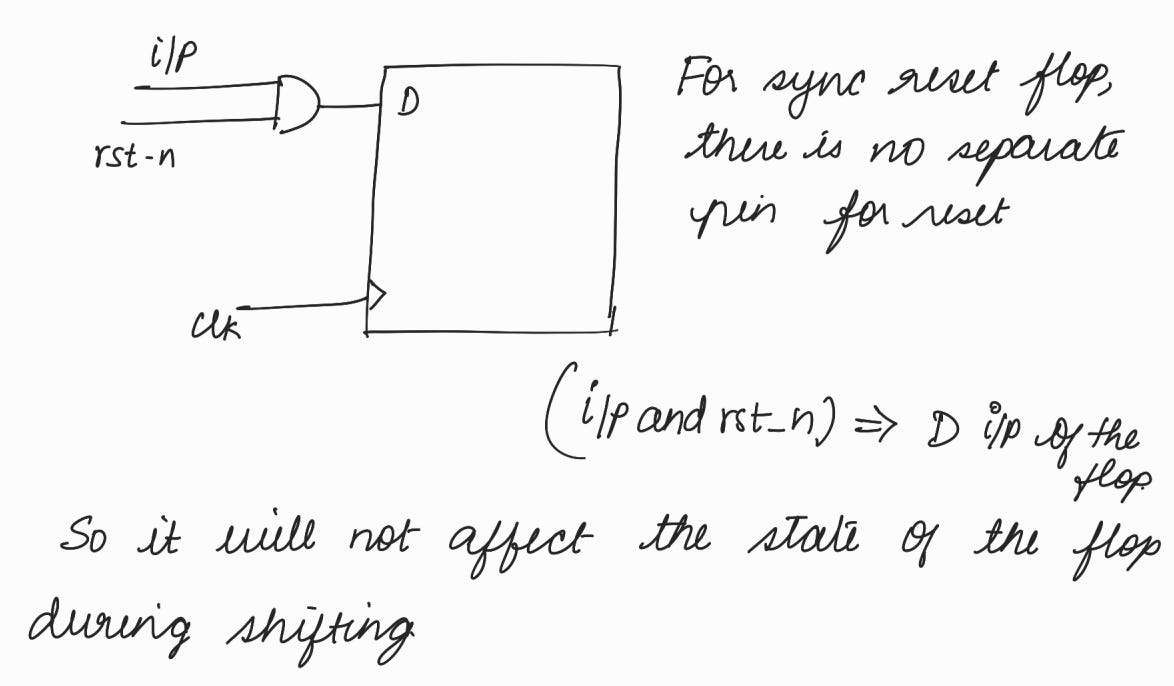

Scenario 2 :

It is an active low reset flop.

It’s reset pin is tied to Vdd. It is getting it’s off-state value. The circuit operates normally.

So it is not pointed as S1 violation.

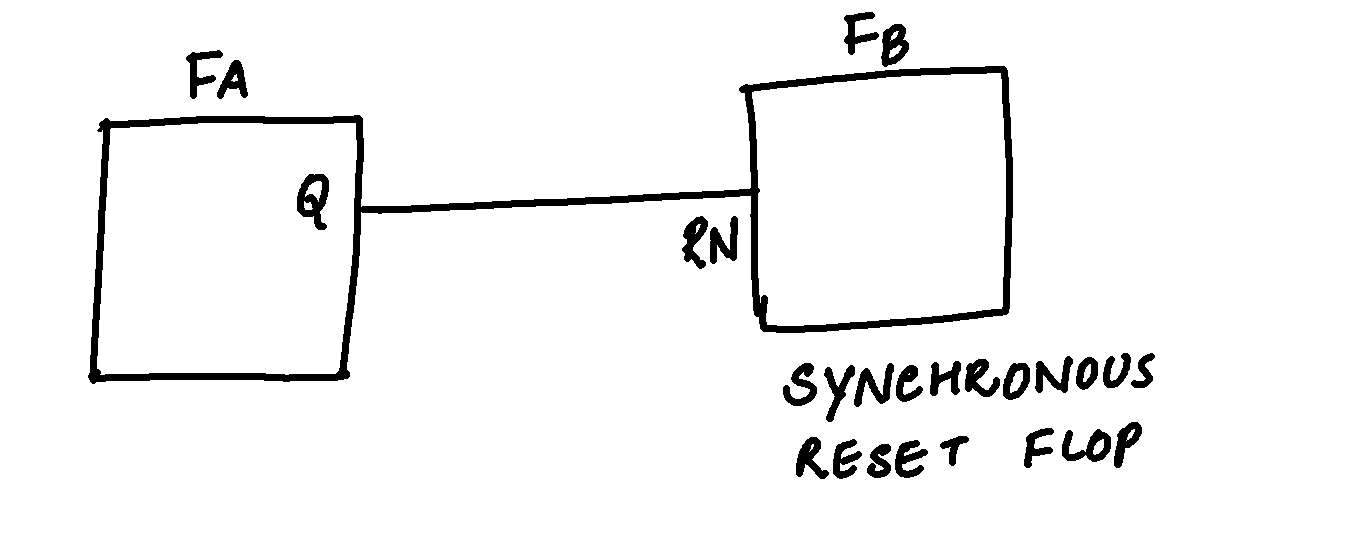

Q6 : Consider the below scenario :

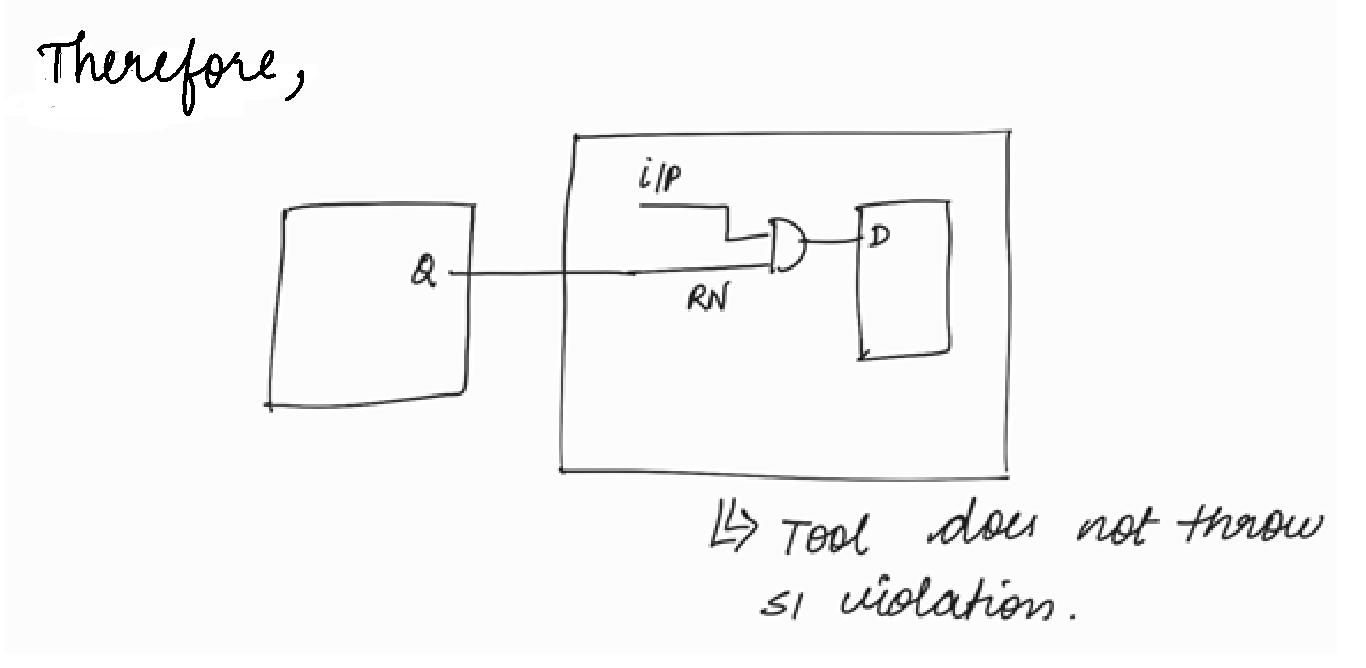

The reset pin of FB is controlled by FA’s Q. But Tessent tool doesn’t point this as S1 violation.

Why?

Ans :

FB is a synchronous reset flop.

We will first explore the difference between Synchronous and Asynchronous Reset flops.

In the case of Asynchronous Reset flop

So we need to fix the S1 violation

< < The explanation of this fix is explored in Scan DRC (part 1) > >

In the case of Synchronous Reset flop,

Q7 : What is C3 violation?

Ans :

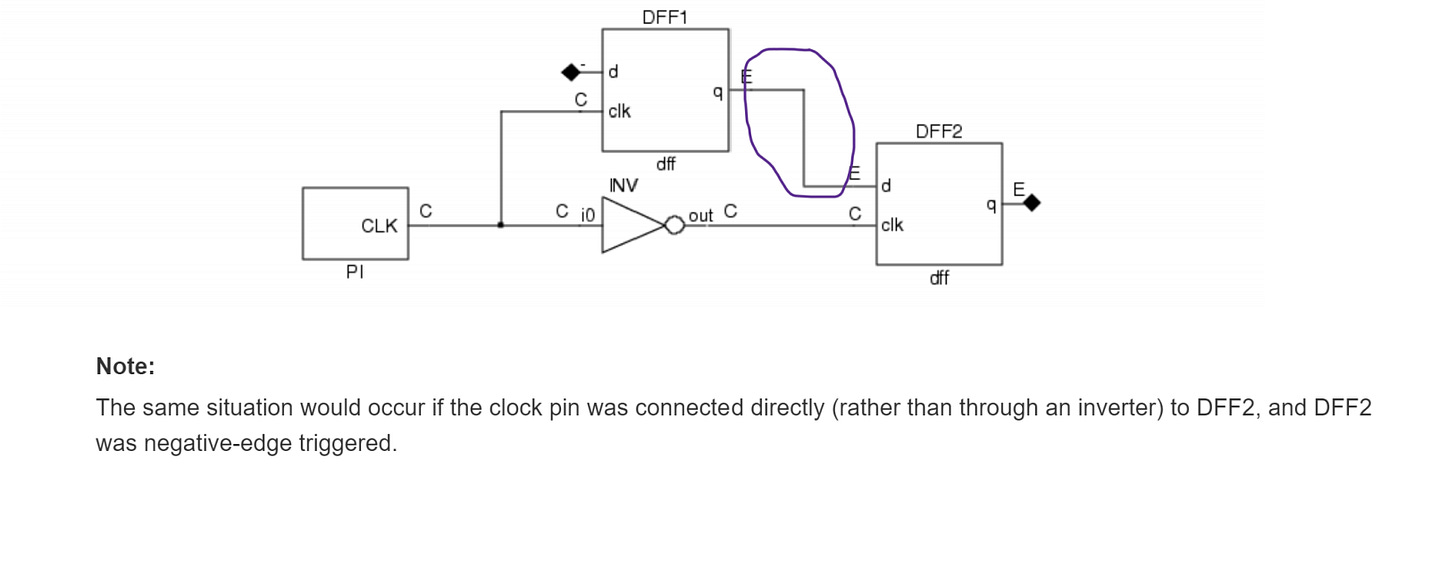

When a positive edge triggered flop’s output goes as the D input of a negative edge triggered flop, it is pointed as C3 violation in Tessent Scan tool.

Image Source : Tessent Scan and ATPG User’s Manual

NOTE :

Whenever we have both positive and negative edge triggered flops, for scan path, it will be taken care as discussed in Problems in Edge Mixing :

• While doing scan chain stitching, the tool will try to keep all negative flops at the starting of the scan chain.

• Suppose if the tool is unable to do so, and if there is a positive ff and then negative ff, it will insert Lock up latch.

For C3, the problem is happening at the D path (marked in violet in the above figure). This can cause problem during capture phase. Failure to address this issue can result in simulation mismatches when we verify the test patterns in a timing-based simulator.

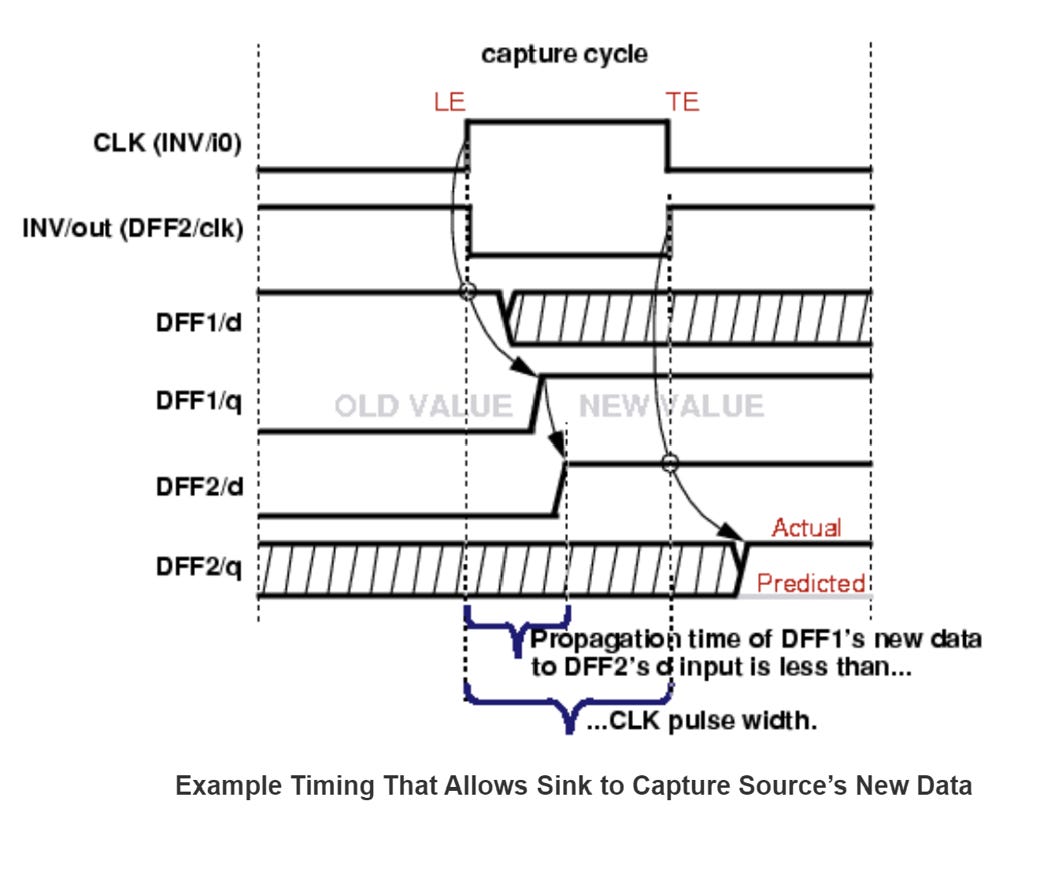

Let’s explore the problem with the help of the below waveform :

Image Source : Tessent Scan and ATPG User’s Manual

Solution of C3 violation :

Command :

set_split_capture_cycle on (Note : This command is given in ATPG run)

When set to on, the tool updates simulation data between clock edges. This “split capture cycling” of data allows the tool to determine correct capture values for trailing edge and level-sensitive state elements, even in the presence of C3 violation.

Q8 : What steps we take while doing scan planning ?

Ans :

We have to decide the following :

To check for which blocks compression is required (if a block is very small, we don’t require compression)

no. of EDT channels and scan chains

Shift frequency

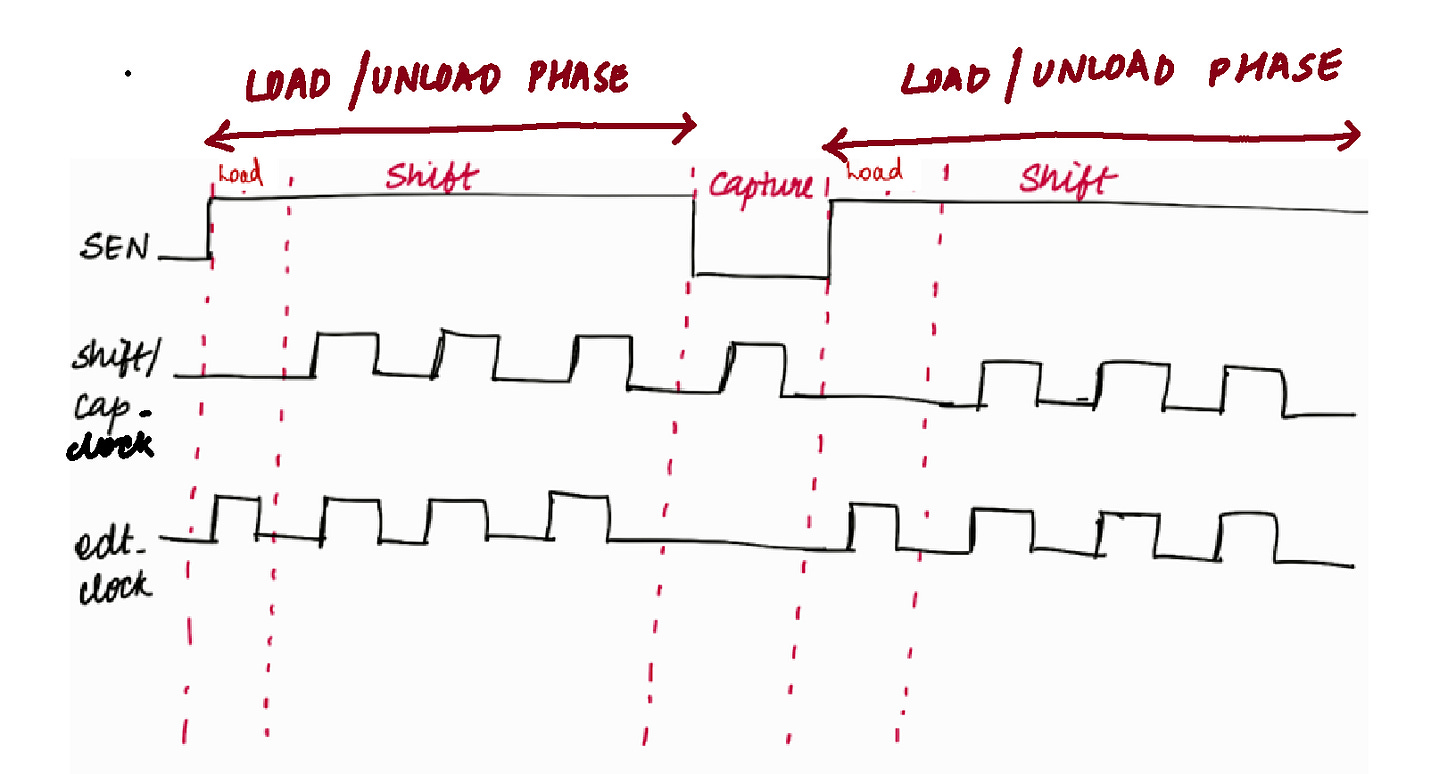

Q9 : How will you create edt_clock and shift_capture clock ?

Ans :

Note :

edt_clock is the clock which goes to the EDT logic flops.

< < To understand EDT logic, please check out my DFT Basics Article #11 to 17 > >shift_capture_clock is the slow frequency clock of the scan flops.

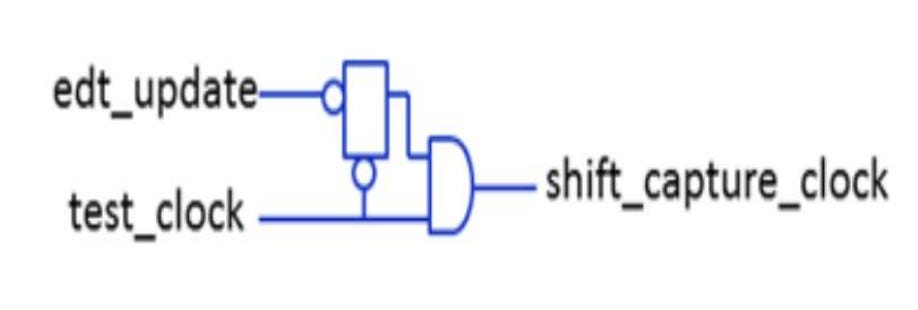

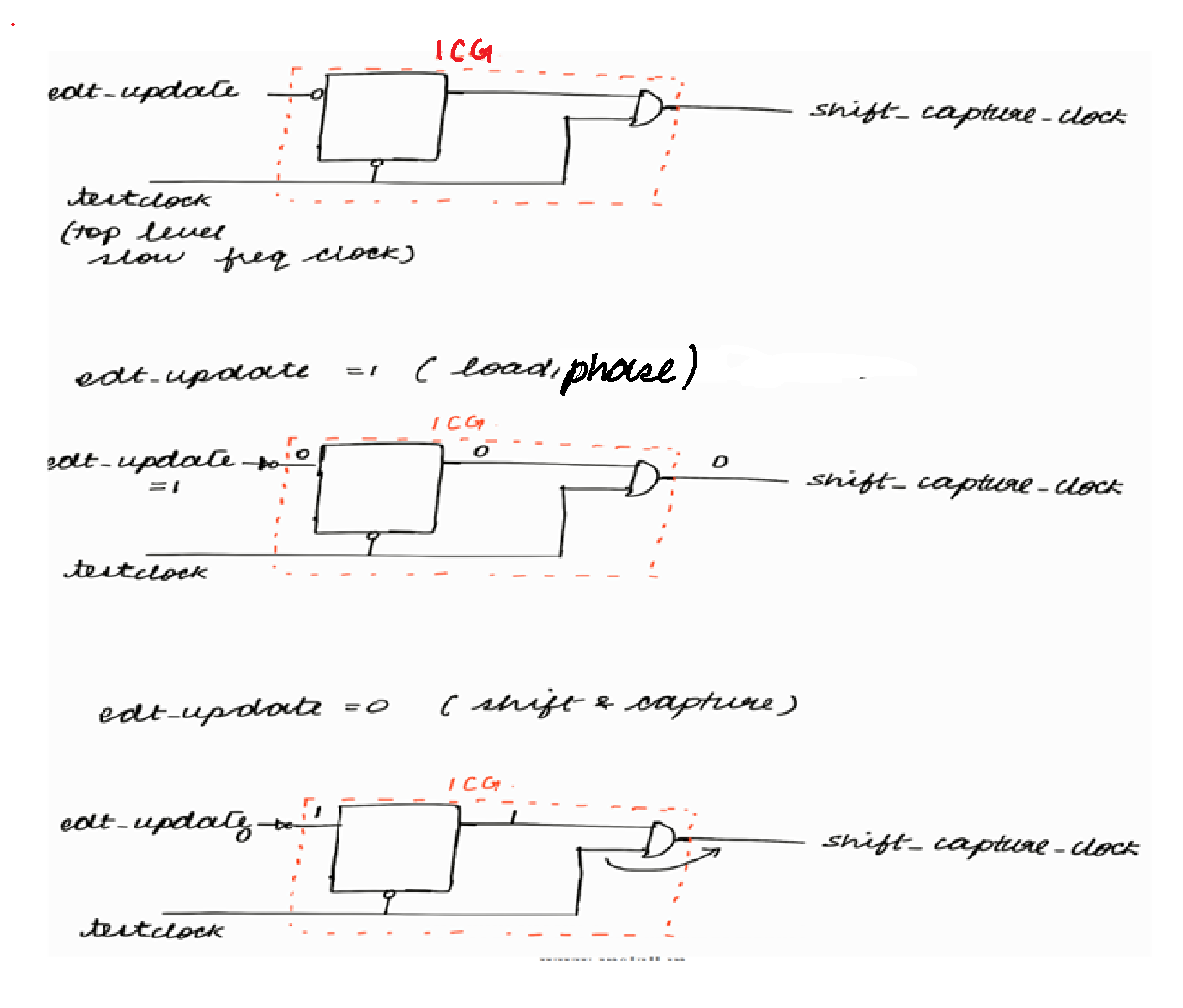

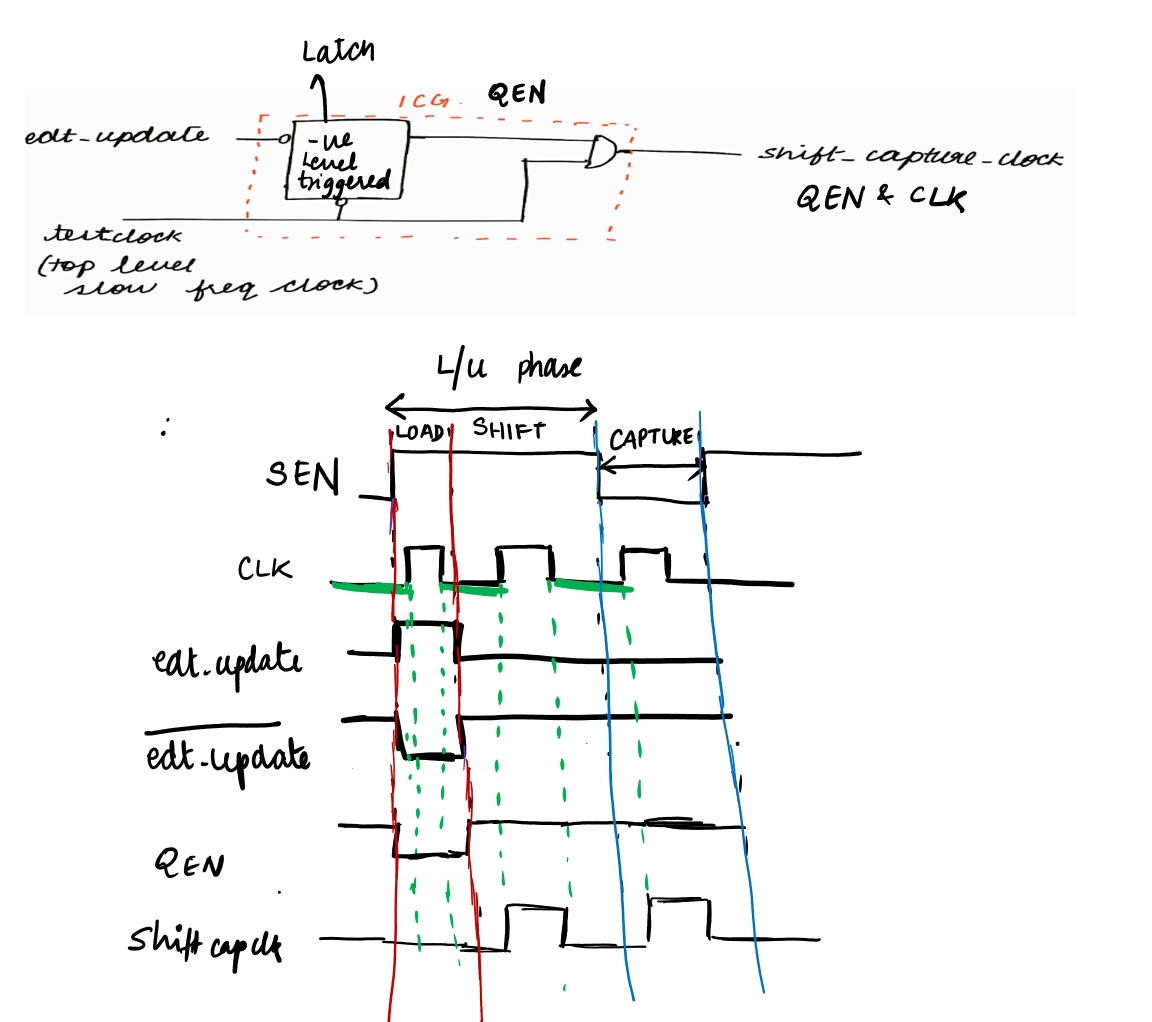

The below structure creates shift_capture_clock

Image Source : Tessent Scan and ATPG User’s Manual

Let’s explore the above structure

Let’s explore the same using a waveform :

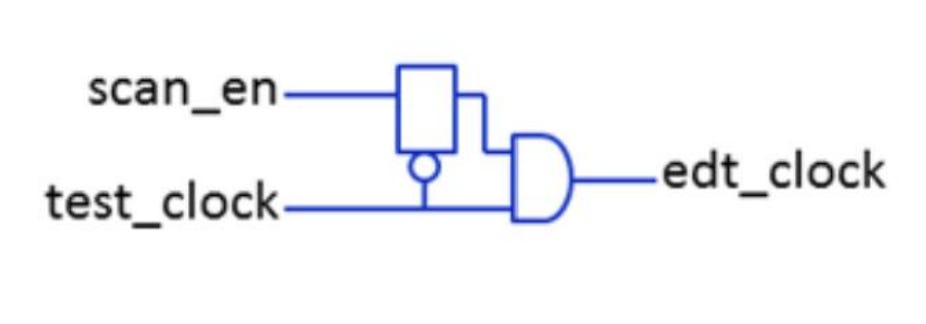

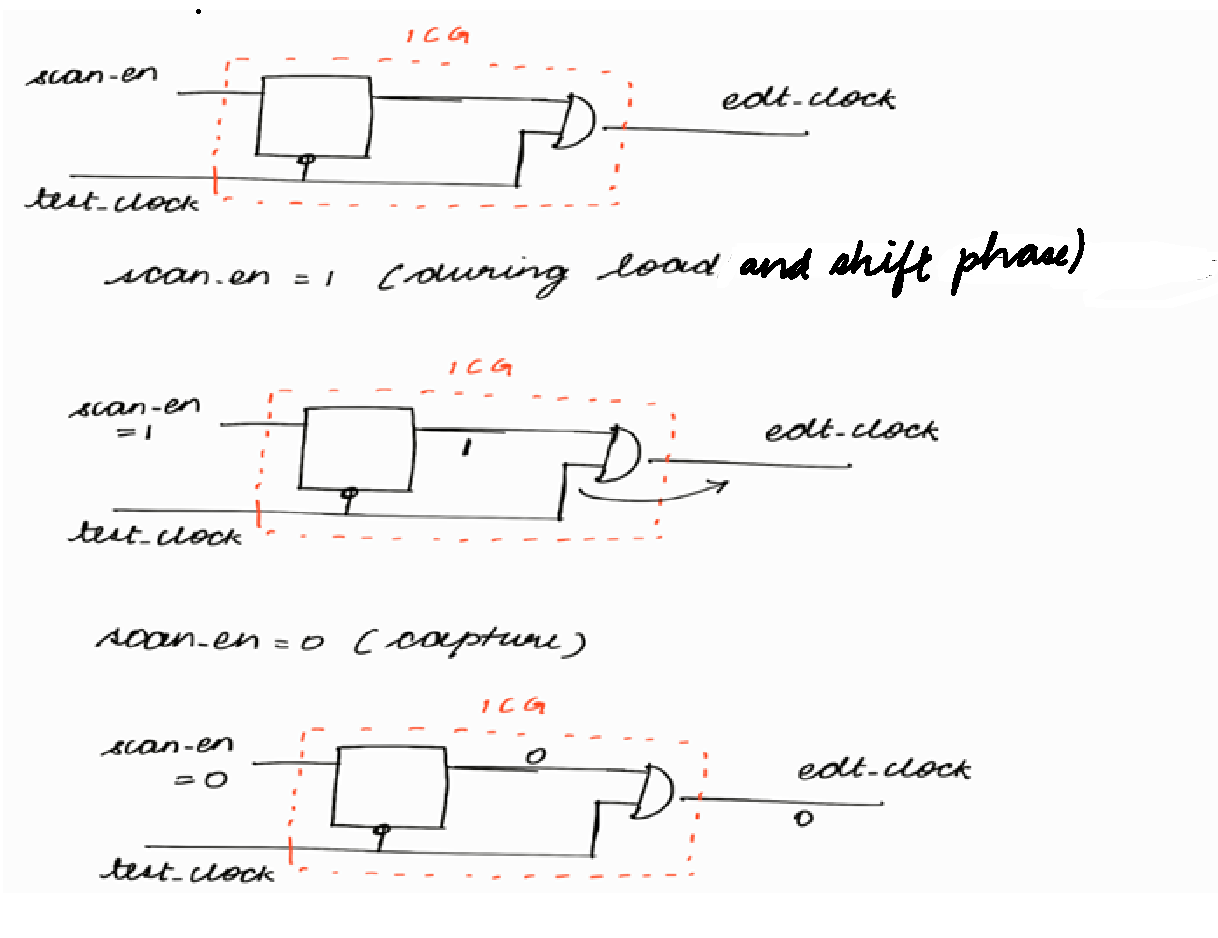

Similarly the below structure creates the edt_clock

Image Source : Tessent Scan and ATPG User’s Manual

Let’s explore the above structure

Q10: Why PD team require scandef file? What will happen if scandef file is not provided to the PD team?

Ans :

For scan chain re-ordering, PD team need scandef file because that file only contains information about which cells can be re-ordered.

If scandef file is not provided to PD team then, scan chain re-ordering can’t be done and it will result in congestion.

We have explored scan chain re-ordering in Scan Chain Re-ordering

References :

Tessent Scan and ATPG User’s Manual

In this blog post, we have explored some of the practical interview questions related to scan insertions and scan compression.

In the next blog of this series, we will explore some application oriented interview questions from ATPG.

Stay Tuned !